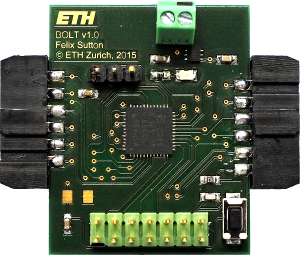

BOLT - A Stateful Processor Interconnect

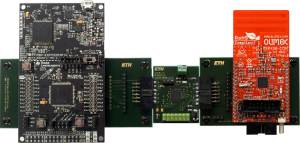

In order to address the ever increasing demands of IoT, we advocate a new architectural blueprint for the design of composable and predictable multi-processor wireless sensing platforms.

BOLT is an ultra-low power processor interconnect that decouples arbitrary application and communication processors with respect to time, power and clock domains. BOLT supports asynchronous message passing with predictable timing characteristics, and therefore making it possible for the system designer to construct highly-customized platforms that are easier to design, implement, debug and maintain.

The BOLT software is available on external pageGithubcall_made.